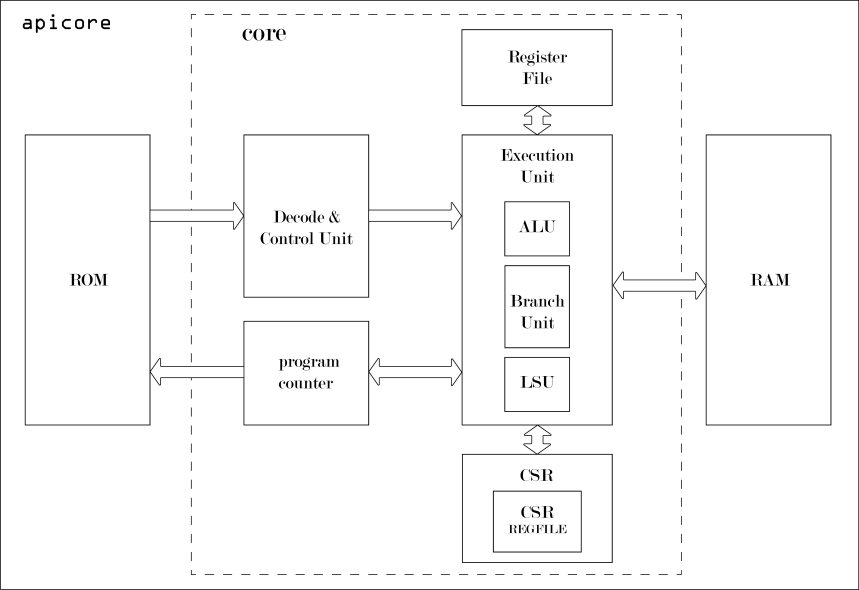

Api Core is a RV32IM core designed in verilog. This was my minor project in my undergraduate degree. We were able to run multiple assembly programs on the core. This core does in-order execution and has a dedicated RAM and ROM section. Program Code are directly written to ROM and the core starts the execution from address 0x0 when booted.

Multiple sections of the core was designed individually which were.

- Decode and Control Unit

- ALU

- Branching Unit

- Load and Store Unit (LSU)

- Register File

- Control and Status Registers

The core was entirely written in Verilog and wrote a simple assembler to translate the assembly core to the machine code.

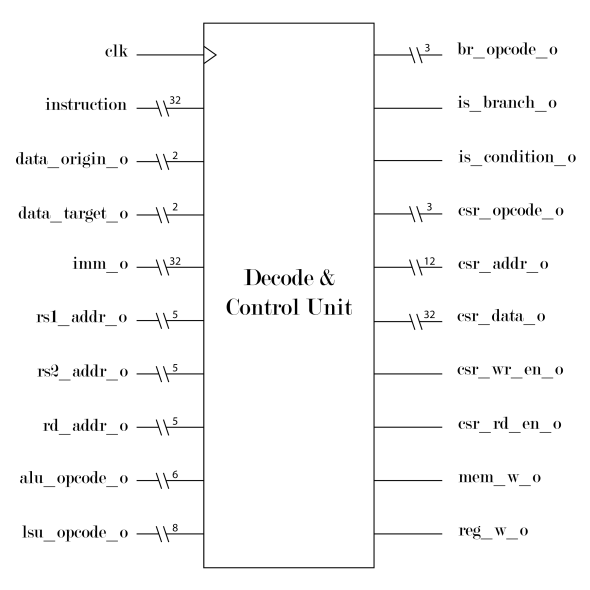

Decode and Control Unit

The Decode and Control unit was responsible for decoding the code fetched from the code memory and generating necessary control signals for the decoded instruction. Here, _0 in the block represents data moving out from the unit.

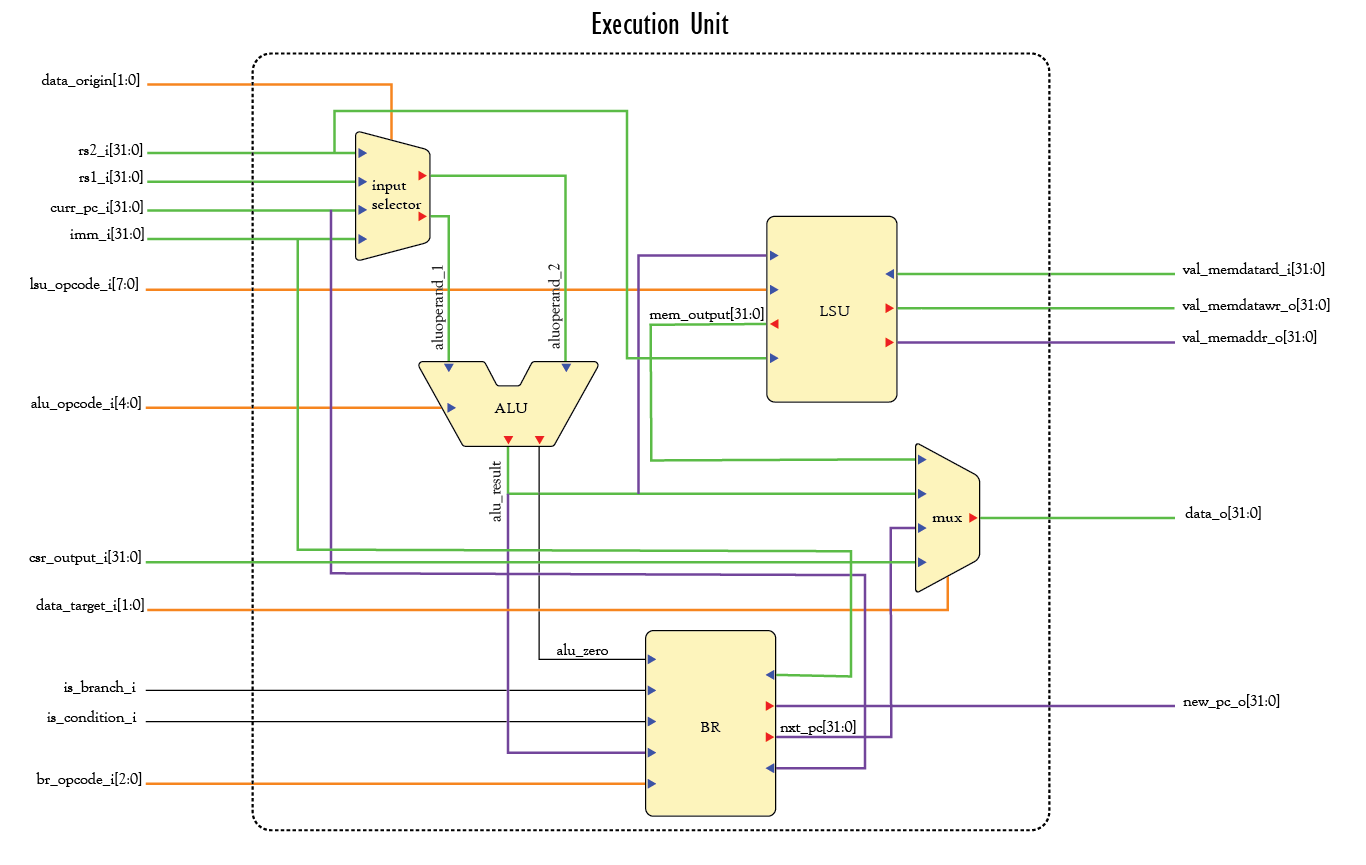

Execution Unit

Execution Unit consisted of Load and Store Unit, Arithmetic and Logic Unit and a Branching unit. It received control signals the previous unit. It's main job is to execute the command in hand. A command may require data for execution which is aided by the LSU and a branch command makes necessary changes to the registers to move to another location in the memory.

I read papers directly provided by the RISC-V foundation to implement this core. Additional details about the project can be gained from the source code.

I wrote a paper which I had defend for my minor project which I have attached here.